ISSN(O): 2319-8753

ISSN(P): 2347-6710

# International Journal of Innovative Research in Science Engineering and Technology (IJIRSET)

(A Monthly, Peer Reviewed, Refereed, Scholarly Indexed, Open Access Journal)

**Impact Factor: 8.699**

Volume 14, Issue 8, August 2025

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

Volume 14, Issue 8, August 2025

|DOI: 10.15680/IJIRSET.2025.1408098|

## Security Enhancement in Systems using 7T Static Random-Access Memory Cell

Dr Reddi Sridevi<sup>1</sup>, Panem Ratnababu<sup>2</sup>

Professor, Dept. of ECE, Sri Vahini Institute of Science, and Technology, Tiruvuru, AP, India<sup>1</sup> PG Scholar, Dept. of ECE, Sri Vahini Institute of Science and Technology, Tiruvuru, AP, India<sup>2</sup>

ABSTRACT: A significant danger to computer security has emerged via the use of power analysis (PA) attacks, which enable covert data extraction by examining the current being used by the power source of the system. Many of these systems rely on embedded memories, often implemented using six-transistor (6T) static random-access memory (SRAM) cells. Conventional SRAM cells are vulnerable to side-channel attacks because the connection among their electrical characterization and written data allows them to be mapped. By integrating an extra transistor into the 6T SRAM cell, as well as two-phase write operations, we believe we may increase the SRAM's resilience and offer enhanced security in the face of these kinds of assaults. An in-house-developed 7T SRAM cell (which uses a 28 nm manufacturing process) outperforms traditional 6T SRAM in terms of reduced write energy standard deviation, achieving nearly 1000X lower variance in write "1" and "0" operations. The cell is capable of decreasing write energy by 39%–53%, and it also has a decrease in write latency of 19%–38% compared to existing power analysis resistance SRAM cells.

**KEYWORDS:** System on chip, Transistors, power analysis, statis random access memory.

#### I. INTRODUCTION

Modern systems-on-chips (SoCs) are designed to tackle the problems of many environments and applications. Starting with a complicated and rather well-protected automobile system, we move on to mobile devices with less resources and finally to a standalone network node. The transmission, processing, and storage of sensitive data is an area where each of these sectors has unique security needs. Consequently, researchers and businesses alike are increasingly worried about the safety of these electronic systems.

Because they take use of private knowledge about the physical behaviour of cryptographic devices, Side Channel Analysis (SCA) attacks pose a significant danger to these devices [1-2]. Because they only necessitate basic hardware and software, Power Analysis (PA) and Electromagnetic Analysis (EMA) assaults are strong forms of SCA [3–11]. The link between a device's internally processed and stored data and an immediate physical measurable quantity (such as radiation or current) can be used in PA and EMA attacks to extract secret or sensitive information.

Important for security, Secured Static Random-Access Memories (SRAM) can be created as a Root-Of-Trust component for storing or boot-loading a used for long-term secrets storage (on-chip SRAM macros), intermediate calculations (L0, L1 cache, Register files, FIFOs, etc.), or several other purposes. Additionally, security primitives including P/T-RNGs, SRAM-PUFs, and seed storage and loading are built using these. The authors in [12] shown that even in a secure-design,' the system's security is compromised by instantiating insecure memory instances, which is a danger associated with employing an insecure memory. They proved that a real-world data-masked system is less secure when using a microprocessor's local register files, shift-registers, and tiny caches (L0 and L1). When sensitive data is exposed to higher-caches, as happens, for example, during a software implementation's load/store operation, this problem becomes more apparent and becomes a bigger difficulty.

It is often more advantageous to implement side-channel protection on low-level cache hierarchies when logic-layer protection is required. Many very large-scale integration (VLSI) system-on-chips (SoCs) [13] rely on low-level caches (e.g., embedded memories) to store data and instructions, and these caches are essential to many cryptographic systems (e.g., smart cards [14] and wireless networks using cryptography algorithms [15]). Consequently, there is paramount relevance in studying and designing protected embedded memory. The 6-transistor (6T) SRAM macrocell is the

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

standard for embedded memory in most systems. Due to the link between the data stored in the memory and the current pulled from the memory supply, traditional 6T SRAM cells are vulnerable to power/electromagnetic analysis assaults [16–17].

This makes them leak important information. Due to the extra devices used to reduce the correlation between the proceed data and the gate's power consumption, designing SCA-resilient digital circuits often results in significant area and power penalties [18]. However, these overheads are unmanageable when it comes to the design of secured embedded memories, which already cause area and power bottlenecks in many SoCs [19-20]. The majority of the literature on secured SRAM implementations has been on bitcell-level solutions, with suggestions for modifying SRAM cells to lessen data leakage from bitcell array supplies. The initial 6T SRAM implementation necessitated the insertion of extra devices, which led to substantial space and power overheads in these implementations. It is crucial to avoid architecturally encrypting or disguising memory content since it imposes substantial overhead and expenses. Lastly, foundries often employ "pushed" design criteria to further shrink the 6T SRAM cell; however, these rules are inapplicable when creating changed bitcells, leading to an even bigger area overhead when attempting to alter a design at the bit-cell level.

#### II. METHODOLOGY

Recently, a new technique was used that employs cryptographic applications in devices where more sensitive information is stored and retrieved. Thus, in contrast to other power analysis methods, the connection of instantaneous current consumption power distribution devices and information leakages is clearly shown in its effect on the power analysis methods of calculating side channel signals. This paper describes a new security-oriented 7T SRAM cell design that includes two-phased write processes and minimizes correlation between written and stored data, and therefore conserves power. In the current 6T SRAM implementation, there is one power gate transistor for each memory cell. The proposed 7T cell will use an extra transistor to increase the total number of transistors, with single energy gate transistors per memory cell. This proposed work would develop a 7T Ram bit cell in 22nm CMOS technology with inline and 8-bit level operations in TANNER EDA Software. It will do so compared to the 6T SRAM bit cell it is replacing, which is also done in 22nm CMOS technology having single bit and 8-bit level operations.

#### 2.1 7T SRAM Design

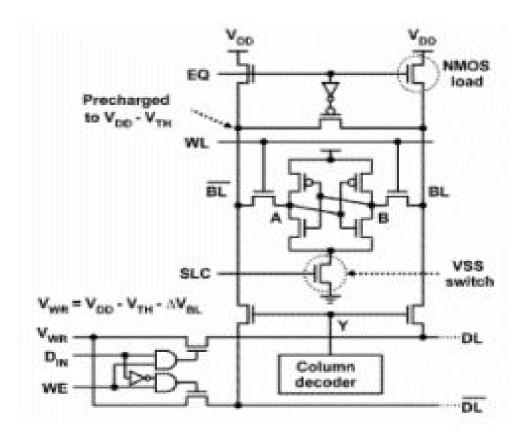

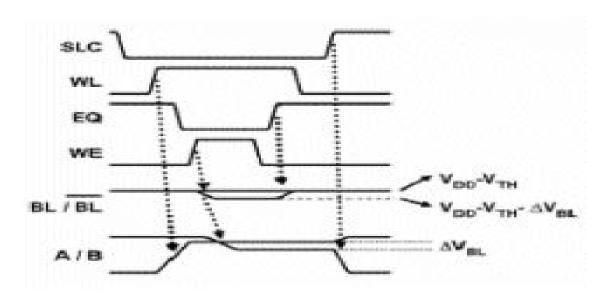

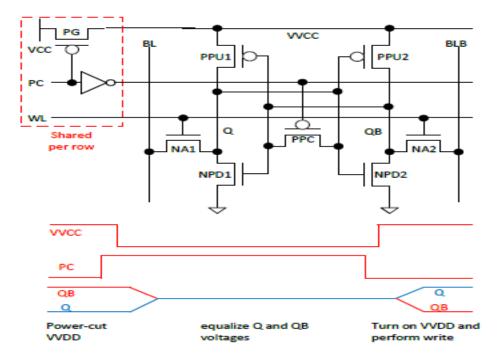

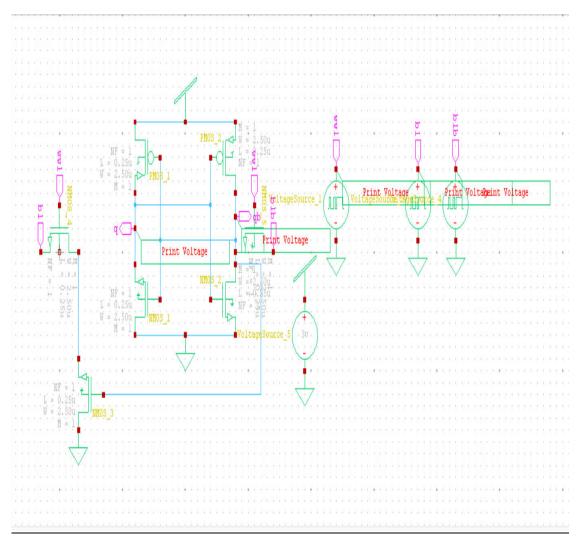

The circuit design and the operating waveform of a proposed cell system are shown in figures 1 and 2. The most notable aspect of the method is that an extra nMOS transistor has been added between the output of driver nMOS transistor of a memory cell and the source of the memory cell's nMOS transistors, which allows modest swings of bit lines during a write operation. This nMOS, which is in addition to the remainder of this document, is referred to as Vss. When applied with a nMOS load transistor, a bit line is precharged to  $V_{DD} - V_{TN}$ . Afterwards, in a write operation where Vtn and DBL are the threshold voltage of a load nMOS and writing swing, respectively, the bit line is pushed down to  $V_{DD} - V_{TN} - DBL$ . Because the cells' access transistors cannot turn on during the write process, the duty cycle level should not be set to  $V_{DD}$ . Because there is no disparity between the operating voltage of bit lines in read phases which in write cycles, there is no extra power consumption if the read and write cycles alternate. SLC and WL are synced before the switch  $V_{SS}$  is switched off; this causes  $V_{SS}$  to be shut off before WL is at the highest point during a write cycle. The driver nMOS transistors will not draw current when the word line is active due of the switch.

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

Figure 1. Overall Architecture of 7T SRAM cell

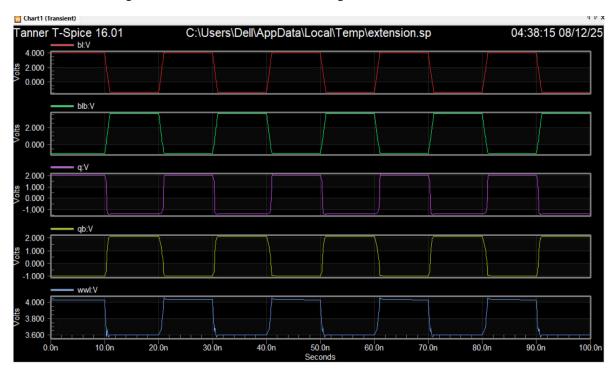

Figure 2. Write Cycle waveform

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

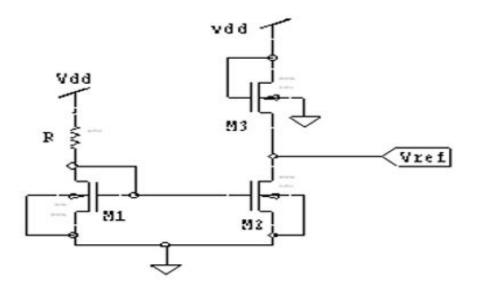

Once WL reaches a low point, SLC climbs back to high, and the swing on small-swing data is exaggerated until it fills the gap within a cell. To enable the cells to communicate with the active word-line, the cells that are linked to the word-line should be in a write cycle. For example, data stored in 192 cells becomes unstable while 64 cells are written if the numbers of cells linked to a word-line and to an SLC signal line are 64 and 256, respectively. In Fig. 3, you can see a dc-dc converter working with a voltage reference generator to bring the voltage level of  $V_{dd} - V_{tn} - DBL$  to the level indicated.

Figure 3. Write Voltage Generation Design

Each bit line receives voltage from the  $V_{wr}$  converter through the write circuit. The static power consumption of the voltage generator is quite high, but one generator is sufficient for the whole SRAM chip and the power overhead is insignificant.

By setting the source terminal of the cell driver nMOS transistor floating in write cycles, both the proposed 7T and the driving source line (DSL) cell [3] accomplish small-swing write operation. In contrast to the DSL system, the primary benefit of the suggested design is that it does not need half- prec-harging of bit lines, and it produces positive voltage. As a way to boost the current going to the nMOS transistor, a negative voltage is applied to the source node of the cell driver nMOS transistor during a read cycle. In devices with increased feature size, this causes the gate oxide of the nMOS transistor to be overstressed, resulting in decreased reliability. Pre-charging the bitlines may be avoided since it is utilized in the HS architecture. That is also beneficial because when the connected in series voltage level drops, the write error rate rises. This latter method is referred to as the "Switched Virtual GND Level" or SVGL (short for "Switched Virtual GND Level" or SVGL). Our approach is very different from the SVGL one in that way. To raise the transistors' operating voltage during write cycles, a source terminal of cell driver nMOS transistors is linked to a virtual-GND line, and its voltage is increased from ground level. A virtual-GND line works in tandem with a bitline in the SVGL scheme, while an SLC signal line travels alongside a wordline in the SAC approach. Since the virtual GND line is often longer than just a local wordline, the overhead in terms of delay, power, and area of driving the virtual GND line is considerable compared to the cost, power, and area of driving the SLC signal line. Another factor is that when the bit width is set to 8-bits, the number of active virtual ground lines is equal to the number of active SLC signal lines, while the frequency of activated virtual ground lines is equivalent to the number of activated virtual ground lines. Thus, the SAC (system in a May) system can have reduced voltage and faster speed than the SVGL (system in a Can) system.

#### 2.2 Cell Design Consideration

In the proposed method, read latency, noise margin, and cell area are the most important considerations in cell design. It is mentioned beforehand that there are trade-offs between three design limits of the switch  $V_{ss}$  to b and N. This circuit

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

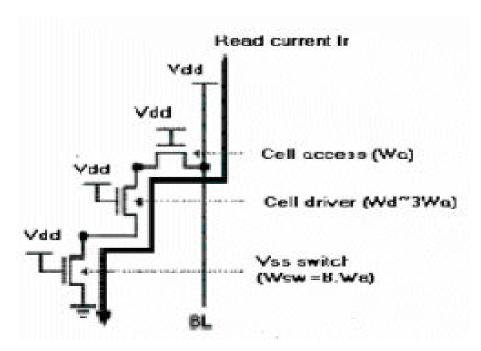

is from Figure 4 which illustrates the intended cell in a read cycle. There are seven nMOS transistors located along the read current route. These three transistors constitute a cell access transistors, a cell driver fets, and the switch's Vss. The first important design parameter b is found by defining b as the ratio of Wsw to Wd. Because the definition of B in this instance is technological-specific, any future debates about the field of technology may apply to any node in the technology tree. When  $W_d$  is set to  $3W_a$  in a typical six-transistor cell, b is practically limitless. Read current or static noise margins will be reduced by the installation of the switch having a finite value. Thus, it's obvious that greater read latency and noise margin result from bigger size, but the maximum value is limited by size restrictions. The second critical parameter N, pertains to a switch layout problem. Since overhead area takes up more than 20 percent of the space, you cannot put the switch cell by cell. The more cells in the same neighborhood, the more a common resource should be spread.

Figure 4. Read Current path of a seven-transistor cell

The three components in each row are responsible for the area penalty. The SLC signal line, the switches itself, and the common - base line which links each cell to the switch are all together referred to as the SLC signal line. This is the most straightforward method to do it, just make the value's maximum equal to the bit width. But in reality, it is difficult to configure in this way because of the following reasons. In figure 4, we see the shared switch structure's read current path. The total current that travels via the common - base line is equal to N while the device is reading.

#### III. RESULTS AND DISCUSSION

As a result of the 6T SRAM cell's information leakage, we propose a modified 7T SRAM cell that incorporates a two-phase write operation, which includes an equalization phase and a write phase, and causes a significant reduction in the amount of current wasted during the write operation, compared to using the 6T SRAM cell directly.

#### 7T SRAM

The suggested 7T SRAM cell is shown in Fig. 5. To prevent power dissipation during the write process, a power gate PMOS transistor (PG) is utilized to turn off the whole memory word  $(VV_{DD})$  voltage supply. The original 6T SRAM system includes a transistor PPC connected to the base of Q and QB that short-circuits Q and QB during the equalization phase. The PC voltage signal is used to turn off PG, thereby removing unnecessary power usage from the power supply, and then to turn on PPC to do voltage equalization between Q and QB. When the write process occurs in

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

its second phase, PC is discharged to charge  $VV_{DD}$ , turn off PPC, and then is charged to transfer data from BL and BLB to Q and QB.

Figure 5. Basic operation of 7T SRAM Cell

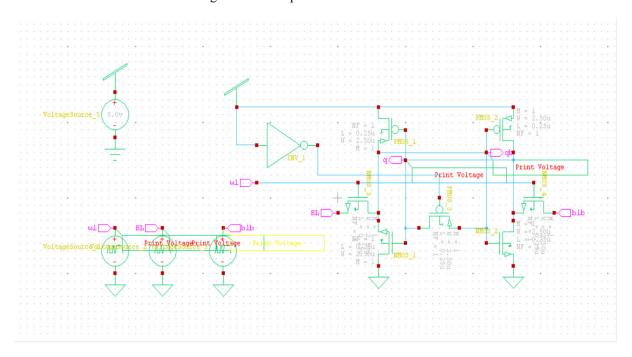

Figure 6. Schematic Model of 7T SRAM

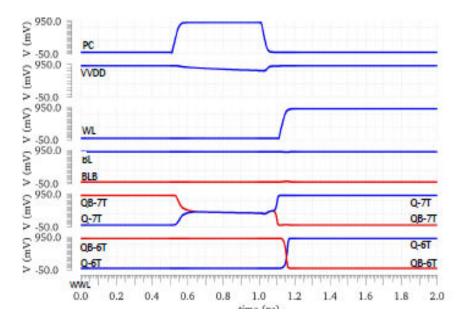

Fig. 7 is a waveform example of a write operation that involves two phases. The top waveform depicts the writing of a '1' into a cell that was previously holding a '0'. In typical 6T SRAM cells, the internal Q and QB voltages are displayed

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

for comparison. Before applying power to the cells in a single word, the PC voltage is first asserted. The increased voltage reduces  $VV_{DD}$ , which causes equalization of the internal Q-7T and QB-7T voltages via charge sharing. This last stage restores  $V_{DD}$  and activates the WL to allow writes to the cell. Set to  $VV_{DD}$  and GND, respectively, the BL and BLB (already in that configuration) are then moved to Q-7T and QB-7T, where they are used to finish the write process. The voltage of the internal cells of a 6T cell, Q-6T and QB-6T, is only altered when the  $W_L$  is asserted, which means the energy of writing '1' and '0' operations is drastically different. The svc

Figure 6. Waveform illustration of the 7T SRAM write operation

Figure 7. Waveforms of the proposed differential 7T SRAM including a replica BL

www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

The area utilized for design of 7T SRAM is shown in table 1.

Table 1. Area utilization for 7T SRAM

| Device            | count |

|-------------------|-------|

| MOSFETs           | 9     |

| MOSFET geometries | 3     |

| Voltage sources   | 4     |

| Subcircuits       | 1     |

| Model definitions | 2     |

| Computed models   | 2     |

| Independent nodes | 4     |

| Boundary nodes    | 5     |

#### Adiabatic 7T SRAM:

The schematic diagram of adiabatic 7T SRAM is shown in figure 8.

Figure 8. Schematic diagram of Adiabatic 7T SRAM

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

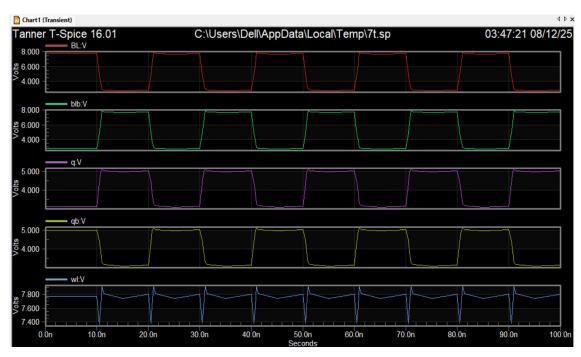

The waveform of the designed adiabatic 7T SRAM is shown in figure 9.

Figure 9. Waveforms of the Adiabatic 7T SRAM including a replica BL and polarity inter change

The area utilized for design of Adiabatic 7T SRAM is shown in table 2.

Table 2. Area utilization for Adiabatic 7T SRAM

| Device            | count |

|-------------------|-------|

| MOSFETs           | 7     |

| MOSFET geometries | 2     |

| Voltage sources   | 4     |

| Subcircuits       | 0     |

| Model definitions | 2     |

| Computed models   | 2     |

| Independent nodes | 5     |

| Boundary nodes    | 5     |

#### **Power Analysis**

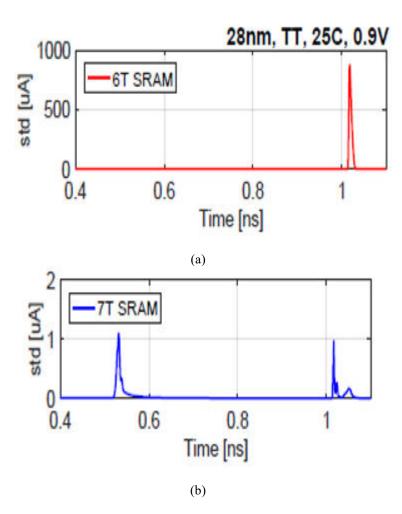

Because the 7T cell has an equalizing, symmetric structure, equalization phase current use is independent of any data previously stored in the cell. The power used prior to the WL assertion is the same whether or whether '1' or '0' had already been stored in the cell. With regards to the write '1' and '0' operations illustrated in Fig. 10(a), nearly similar waveforms are seen because of the two-phase write operation, showing that the information leakage from the currents dissipated in the 7T SRAM cell is non-existent. Fig. 10(b) shows the 1000 Monte Carlo simulations used to produce the write energy scatter plot of the 7T SRAM cell, which was derived using imperfect device matching and process variations. These estimates vary greatly from values obtained for the 6T SRAM cell, which show that the mean energy dissipations for the write '0' and '1' operations are 2.297 fJ and 2.301 fJ with a standard deviation of 0.0345 fJ and 0.353 fJ.

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

The total energy of an m-bit phrase stored in a memory row may be determined by determining the write energy dissipation and the amount of data stored. The total energy dissipation in m-bit words that are stored in an array is proportional to the Hamming value of the stored data, which is given by,

$$E_{w_{word}} = H_w.E_C + (m - H_w).E_{NC}$$

(1)

When m is the word longitude,  $E_C$  and  $E_{NC}$  are written energy dissipations where the data stored inside the cell is altered or unchanged and  $H_w$  is the hamming weight of a word equivalent to the hamming distance provided between the word value and BL voltages.

$$H_w = HD(BL, Q)|= \sum_i (BL_i \neq Q_i)$$

(2)

Writing simulations of 32 distinct  $H_w$  values were performed to 7T and 6T SRAM cells to assess the safety of the 32-bit memory word, and standard deviations between current traces were calculated. The amount of the data leakage is typically estimated by this methodology. The standard deviation curves produced are shown in Fig. 6. The percent overshoot for the 7T SRAM cell was 1.1  $\mu$ A, nearly three magnitude orders lower than for the 6T SRAM cell at 875  $\mu$ A. For power cut and feedback cut Bit cells, comparable maximum deviations were observed in comparison to the 7T cell at 2.1  $\mu$ A and 0.99  $\mu$ A respectively.

Figure 10. Standard Deviation of the current consumption of the SRAM Cell (a) 6T SRAM (b) 7T SRAM Cell

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

The power and delay results achieved for design of 7T SRAM is shown table 3.

Table 3. Power and delay in design of 7T SRAM

| Parameters                  | Value               |

|-----------------------------|---------------------|

| Average Power consumed      | 1.315755 e-014 wats |

| Max power                   | 1.617323e-004       |

| Mini Power                  | 1.273821e-009       |

| Delay in parsing            | 0.05 sec            |

| Delay in setup              | 0.01 sec            |

| Delay in DC operating point | 0.09 sec            |

| Transient Analysis          | 0.01 sec            |

| Overhead                    | 0.92 sec            |

| Total delay                 | 1.08 sec            |

The power and delay results achieved for design of Adiabatic 7T SRAM is shown table 4.

Table 4. Power and delay in design of Adiabatic 7T SRAM

| Parameters                  | Value              |

|-----------------------------|--------------------|

| Average Power consumed      | 6.851908e-013 wats |

| Max power                   | 3.770196e-003      |

| Mini Power                  | 1.655326e-008      |

| Delay in parsing            | 0.05 sec           |

| Delay in setup              | 0.02 sec           |

| Delay in DC operating point | 0.07 sec           |

| Transient Analysis          | 0.01 sec           |

| Overhead                    | 0.82 sec           |

| Total delay                 | 0.97 sec           |

#### IV. CONCLUSION

Incorporated memories with 6T SRAM screens occupy a significant part of cryptographic systems, which may store secret data; specific design measures are necessary to provide resilience against PA assaults. In this article we presented a new SRAM 7T cell consisting of an extra PMOS transistor that was integrated in the original 6T SRAM execution and a sequence operation to substantially decrease the connection between the energy used and the written data. The suggested 7T Ram cell achieves an energy correlation of more than 1000 lower than traditional 6T SRAM. In addition, the suggested 7T SRAM achieves 39 percent–53 percent reduced energy dissipation using a voltage leveling mechanism during pre-charges during written operation and 19 percent–38 percent less write time than existing PA-resistant SRAM bit.

#### REFERENCES

- [1] P. Kocher, J. Jaffe, B. Jun, and P. Rohatgi, "Introduction to differential power analysis," Journal of Cryptographic Engineering, vol. 1, no. 1, pp. 5–27, 2011.

- [2] S. Mangard and A. Y. Poschmann, Constructive Side-Channel Analysis and Secure Design. Springer, 2015.

- [3] M. Alioto, L. Giancane, G. Scotti, and A. Trifiletti, "Leakage power analysis attacks: A novel class of attacks to nano-meter cryptographic circuits," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 2, pp. 355–367, 2010.

- [4] M. Alioto, S. Bongiovanni, M. Djukanovic, G. Scotti, and A. Trifiletti, "Effectiveness of leakage power analysis attacks on dpa-resistant logic styles under process variations," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 61, no. 2, pp. 429–442, 2014.

- [5] I. Levi, O. Keren, and A. Fish, "Data-dependent delays as a barrier against power attacks," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 8, pp. 2069–2078, 2015.

|www.ijirset.com | A Monthly, Peer Reviewed & Refereed Journal | e-ISSN: 2319-8753 | p-ISSN: 2347-6710 |

#### Volume 14, Issue 8, August 2025

#### |DOI: 10.15680/IJIRSET.2025.1408098|

- [6] I. Levi, D. Bellizia, and F.-X. Standaert, "Reducing a masked implementation's effective security order with setup manipulations," IACR Transactions on Cryptographic Hardware and Embedded Systems, pp. 293–317, 2019.

- [7] M. Avital, H. Dagan, I. Levi, O. Keren, and A. Fish, "Dpa-secured quasi-adiabatic logic (sqal) for low-power passive rfid tags employing s-boxes," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 1, pp. 149–156, 2015.

- [8] R. Giterman, M. Vicentowski, I. Levi, Y.Weizman, O. Keren, and A. Fish, "Leakage power attack-resilient symmetrical 8T SRAM cell," IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, no. 99, pp. 1–5, 2018.

- [9] R. Giterman, O. Keren, and A. Fish, "A 7t security oriented SRAM bit-cell," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 8, pp. 1396–1400, 2018.

- [10] R. Giterman, M. Wicentowski, O. Chertkow, I. Sever, I. Kehati, Y. Weizman, O. Keren, and A. Fish, "Power analysis resilient sram design implemented with a 1% area overhead impedance randomization unit for security applications," in ESSCIRC 2019-IEEE 45th European Solid State Circuits Conference (ESSCIRC). IEEE, 2019, pp. 69–72.

- [11] R. Giterman, I. Levi, Y.Weizman, O. Keren, A. Fish, and M.Wicentowski, "Secured memory," Patent WO2 019 111 260A1.

- [12] S. Gao, B. Marshall, D. Page, and E. Oswald, "Share-slicing: Friend or foe?" IACR Transactions on Cryptographic Hardware and Embedded Systems, pp. 152–174, 2020.

- [13] ITRS, "International Technology Roadmap for Semiconductors 2015 Edition," 2015. [Online]. Available: <a href="http://www.itrs2.net">http://www.itrs2.net</a>

- [14] M. Neve, E. Peeters, D. Samyde, and J.-J. Quisquater, "Memories: a survey of their secure uses in smart cards," in Security in Storage Workshop, 2003. SISW'03. Proceedings of the Second IEEE International. IEEE, 2003, pp. 62–62.

- [15] W. Liu, R. Luo, and H. Yang, "Cryptography overhead evaluation and analysis for wireless sensor networks," in Communications and Mobile Computing, 2009. CMC'09. WRI International Conference on, vol. 3. IEEE, 2009, pp. 496–501.

- [16] V. Roži'c, W. Dehaene, and I. Verbauwhede, "Design solutions for securing sram cell against power analysis," in 2012 IEEE International Symposium on Hardware-Oriented Security and Trust. IEEE, 2012, pp. 122–127.

- [17] E. Konur et al., "Power analysis resistant SRAM," in 2006World Automation Congress. IEEE, 2006, pp. 1-6.

- [18] C. Tokunaga and D. Blaauw, "Secure as engine with a local switched capacitor current equalizer," in 2009 IEEE International Solid-State Circuits Conference-Digest of Technical Papers. IEEE, 2009, pp. 64–65.

- [19] Y.-H. Chen, T. Krishna, J. S. Emer, and V. Sze, "Eyeriss: An energy efficient reconfigurable accelerator for deep convolutional neural networks," IEEE Journal of Solid-State Circuits, vol. 52, no. 1, pp. 127–138, 2017.

- [20] P. N. Whatmough, S. K. Lee, H. Lee, S. Rama, D. Brooks, and G.-Y. Wei, "14.3 a 28nm soc with a 1.2 ghz 568nj/prediction sparse deep-neural network engine with> 0.1 timing error rate tolerance for IOT applications," in 2017 IEEE International Solid-State Circuits Conference (ISSCC). IEEE, 2017, pp. 242–243.

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

9940 572 462 🔯 6381 907 438 🔀 ijirset@gmail.com